- 您现在的位置:买卖IC网 > Sheet目录327 > HW-SPAR3AN-SK-UNI-G (Xilinx Inc)KIT STARTER SPARTAN-3 AN

R

Chapter 13

DDR2 SDRAM

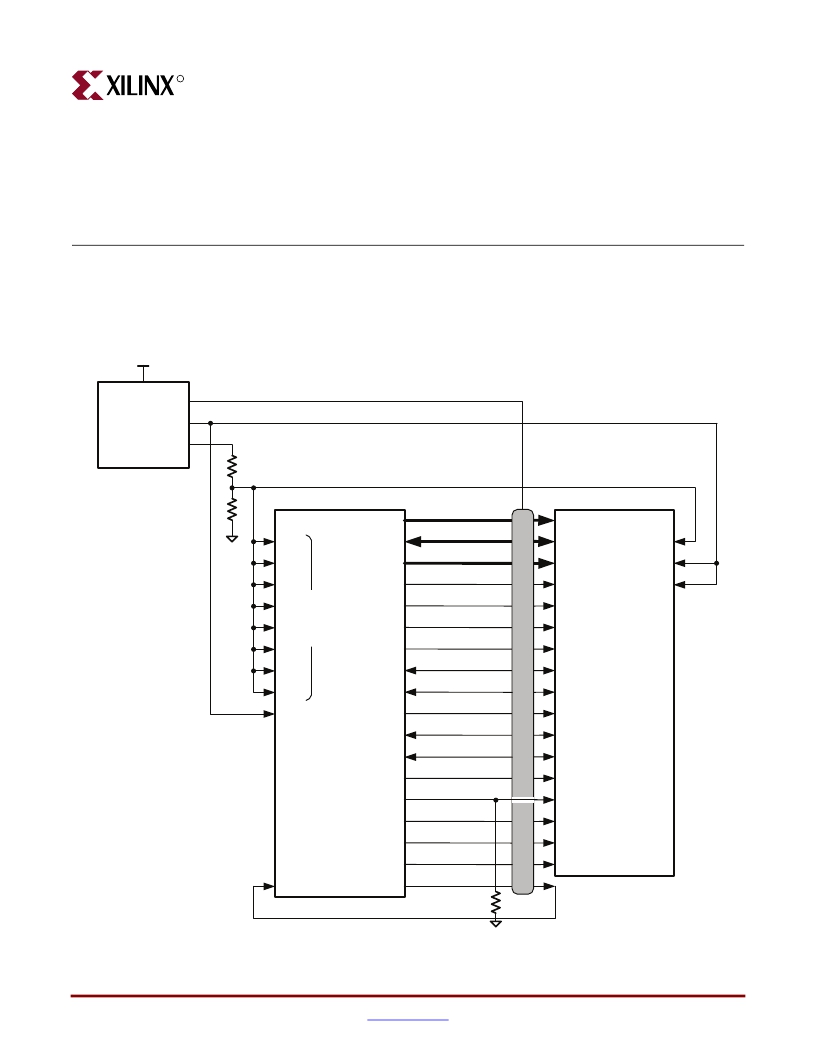

The Spartan ? -3A/3AN FPGA Starter Kit board includes a 512 Mbit (32M x 16) Micron

Technology DDR2 SDRAM (MT47H32M16) with a 16-bit data interface, as shown in

Figure 13-1 .

5.0V

REG2

SW1

SW2

LDO2

0.9V

1.8V

1.8V

(SSTL_18 Termination Voltage)

(DDR2 SDRAM Supply Voltage)

National

Semiconductor

LP3906

Regulator

0.9V

(SSTL_18 Reference Voltage)

FPGA

SD_A<15:0>

See Table

Micron 512Mb

DDR2 SDRAM

A[12:0 ]

(H7)

(J1)

(J8)

(L8)

(N1)

(R6)

(T1)

(T6)

VCCO_3

See Table

See Table

(M3)

(M4)

(N4)

(E3)

(J5)

(K6)

(J3)

(K2)

(K3)

(M5)

(N3)

(M2)

(M1)

(P1)

SD_DQ<15:0>

SD_BA<2:0>

SD_RAS

SD_CAS

SD_WE

SD_UDM

SD_UDQS_N

SD_UDQS_P

SD_LDM

SD_LDQS_N

SD_LDQS_P

SD_CS

SD_CKE

SD_CK_N

SD_CK_P

SD_ODT

DQ[15:0]

BA[1:0]

RAS#

CAS#

WE#

UDM

UDQS#

UDQS

LDM

LDQS#

LDQS

CS#

CKE

CK#

CK

ODT

VREF

VDD

VDDQ

(H4)

SD_LOOP

(H3)

UG334_c13_01_052407

Figure 13-1:

FPGA Interface to Micron 512 Mbit DDR2 SDRAM

Spartan-3A/3AN FPGA Starter Kit Board User Guide www.xilinx.com

UG334 (v1.1) June 19, 2008

107

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HW-V4-ML403-UNI-G-J

EVALUATION PLATFORM VIRTEX-4

HW-V4-ML405-UNI-G-J

EVALUATION PLATFORM VIRTEX-4

HW-V4-ML410-UNI-G-J

EVALUATION PLATFORM VIRTEX-4

HW-V5-ML501-UNI-G

EVALUATION PLATFORM VIRTEX-5

HW-V5-ML507-UNI-G

EVAL PLATFORM V5 FXT

HW-V5-ML550-UNI-G

EVALUATION PLATFORM VIRTEX-5

HW-V5-ML555-G

BOARD EVAL FOR VIRTEX-5 ML555

HW-V5-ML561-UNI-G

EVALUATION PLATFORM VIRTEX-5

相关代理商/技术参数

HW-SPAR3AN-SK-UNI-G-J

功能描述:KIT STARTER SPARTAN-3 AN RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Spartan®-3AN 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

HW-SPAR3A-SK-UNI-G

功能描述:KIT STARTER W/SPARTAN-3A RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Spartan®-3A 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

HW-SPAR3A-SK-UNI-G-J

功能描述:KIT STARTER W/SPARTAN-3A RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Spartan®-3A 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

HW-SPAR3-CPLD-DK

功能描述:STARTER KIT BUNDLE SPARTAN3/CPLD RoHS:否 类别:编程器,开发系统 >> 过时/停产零件编号 系列:- 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

HW-SPAR3-CPLD-DK-J

功能描述:KIT HDWR FOR SPARTAN3/CPLD-JAPAN RoHS:否 类别:编程器,开发系统 >> 过时/停产零件编号 系列:- 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

HW-SPAR3E-DISP-DK-UNI-G

功能描述:KIT DEV SPARTAN3E DISPLAY RoHS:是 类别:编程器,开发系统 >> 过时/停产零件编号 系列:Spartan®-3E 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

HW-SPAR3E-DISP-DK-UNI-G-PROMO

功能描述:KIT DEV SPARTAN3E DISPLAY RoHS:是 类别:编程器,开发系统 >> 过时/停产零件编号 系列:Spartan®-3E 标准包装:1 系列:*

HW-SPAR3E-SK-EC-G

功能描述:KIT STARTER SPARTAN-3E RoHS:是 类别:编程器,开发系统 >> 过时/停产零件编号 系列:- 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP